「Meteor Lake」Deep Dive その2 - Processor Detail

参考記事:

・「Meteor Lake」Deep Dive その4 - GPU、IO & SoC Detail

https://news.mynavi.jp/article/20231010-2789313/

・「Meteor Lake」Deep Dive その3 - AI NPU Detail

https://news.mynavi.jp/article/20231005-2785788/

・「Meteor Lake」Deep Dive その1 - Intel 4 Process Update

https://news.mynavi.jp/article/20230920-2774916/

引き続きMeteor Lakeの構造についてご紹介したい。今回はProcessor Coreの話である。最終的に派生型とかがどの程度あるのかは判らないが、今回発表になったMeteor Lakeの基本構造は、6 P-Core +8 E-Core +2 E-Coreの16コア構成で、P-CoreはHyperThreadingが有効化されているので、OSからは22コア相当として見える形になる(Photo01)。この+2 E-Coreの話はあとでするとして、まずはそれぞれのコアのDetailである。

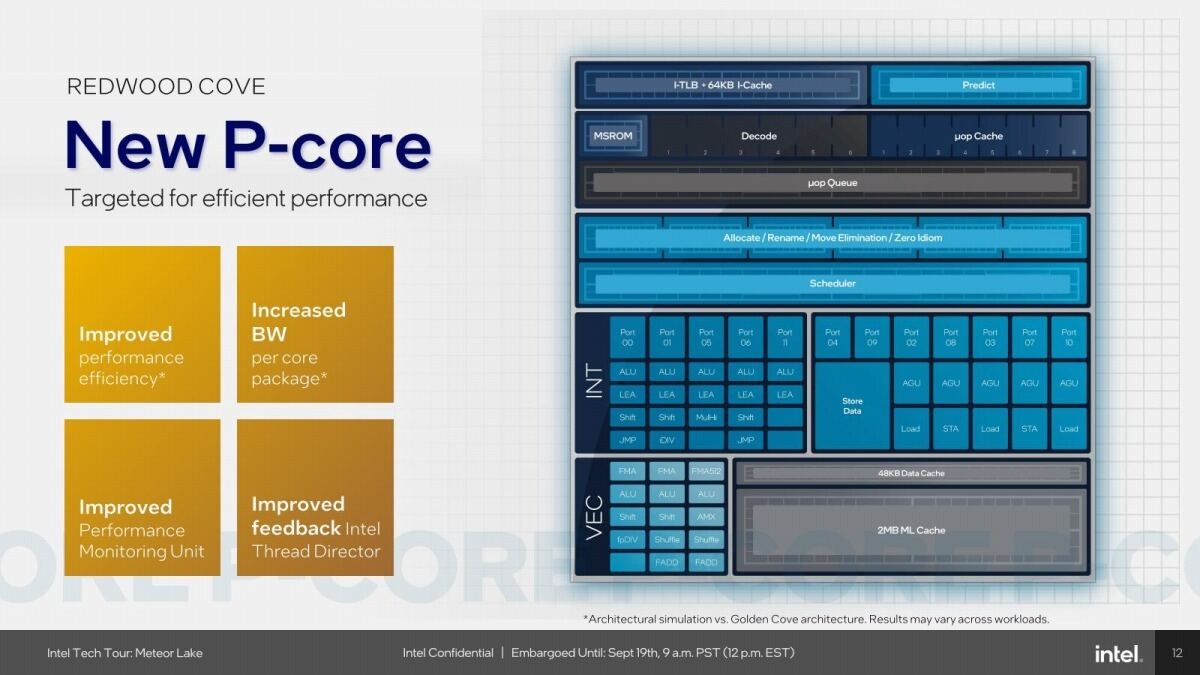

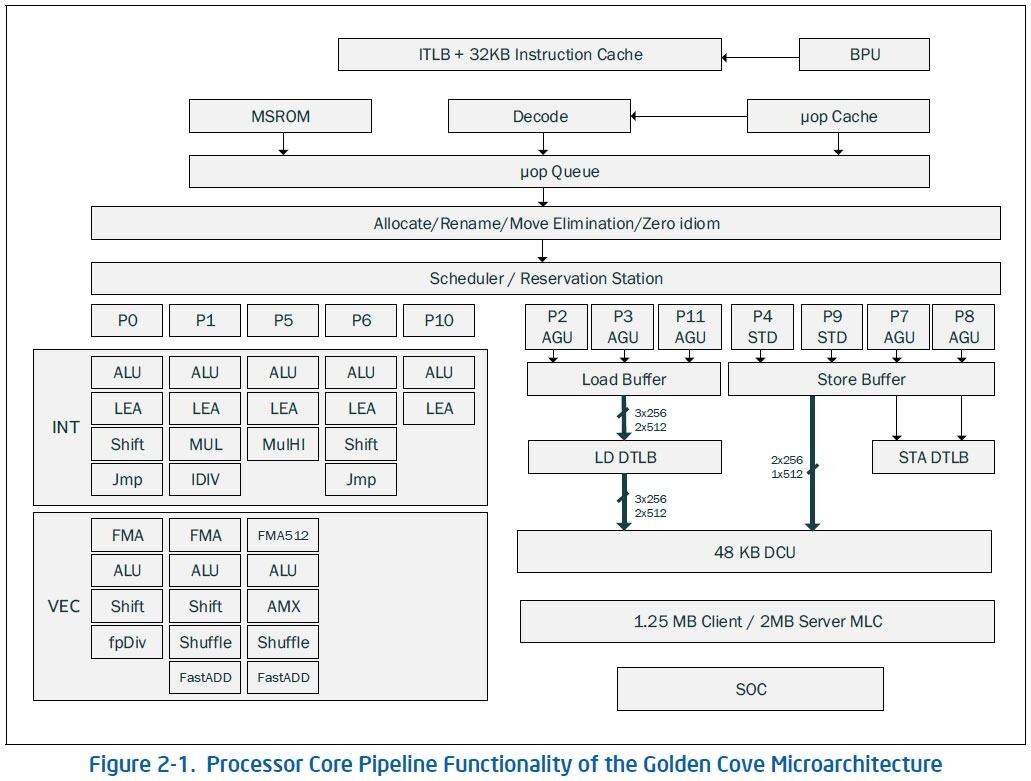

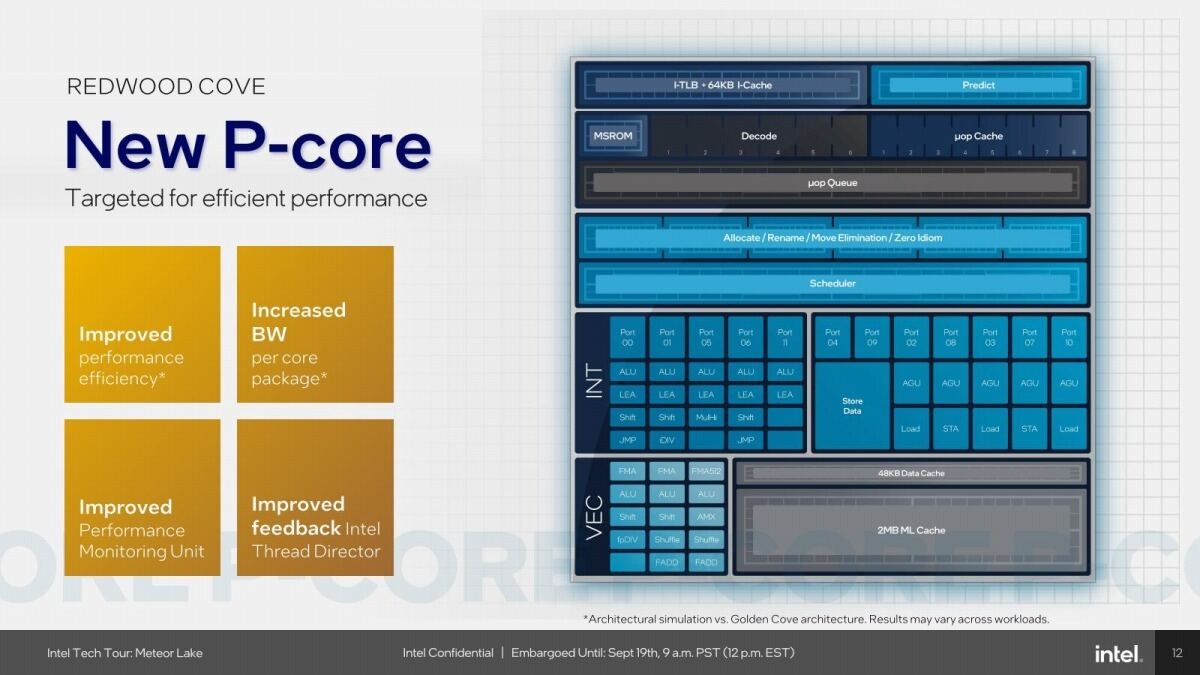

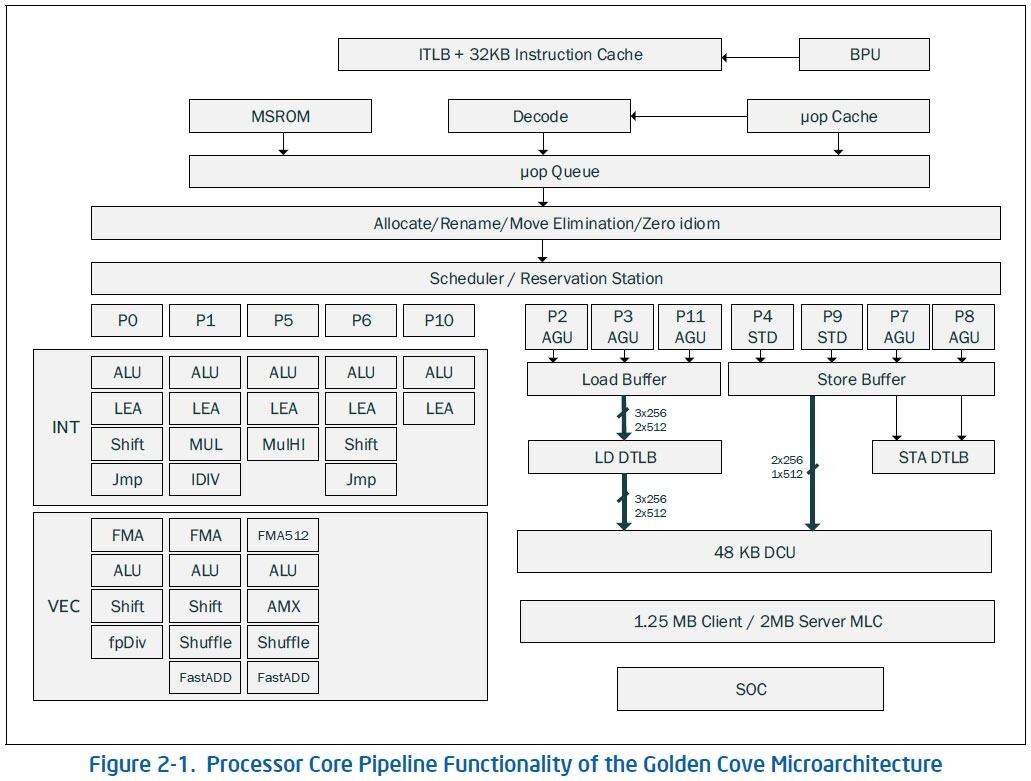

まずP-CoreであるRedwood Coveである。Photo02がそのパイプライン構造の概略であり、Golden Coveと比較してより効率が良くなっている、としている。Golden CoveはAlder Lakeに搭載されたもので、Raptor Lakeに搭載されているRaptor Coveも(キャッシュ容量以外は)Golden Coveと同じとされている。ではそのGolden Coveはどんなだったか? というのがこちら(Photo03)。実のところ、このレベルでいえばGolden CoveとRedwood Coveの違いは

L1命令キャッシュが32KB→64KBに増量

L2キャッシュが1.25MB→2MBに増量

といったあたりで、L2はRaptor Coveの世代ですでに増量されていたことを考えると、要するにL1命令キャッシュが増量された「だけ」という可能性も残る。もちろん実際には細かい命令のLatency削減とかバグ修正とかが行われている可能性はあるが、大きなものではないように思える。New P-coreと書いてはあるものの、基本はGolden Coveの世代を継承しており、Power Efficencyは64KBのL1命令キャッシュか、あとは細かい部分での積み重ねと思われる(プロセスの違いはArchitectual Simulationには反映されないため)。

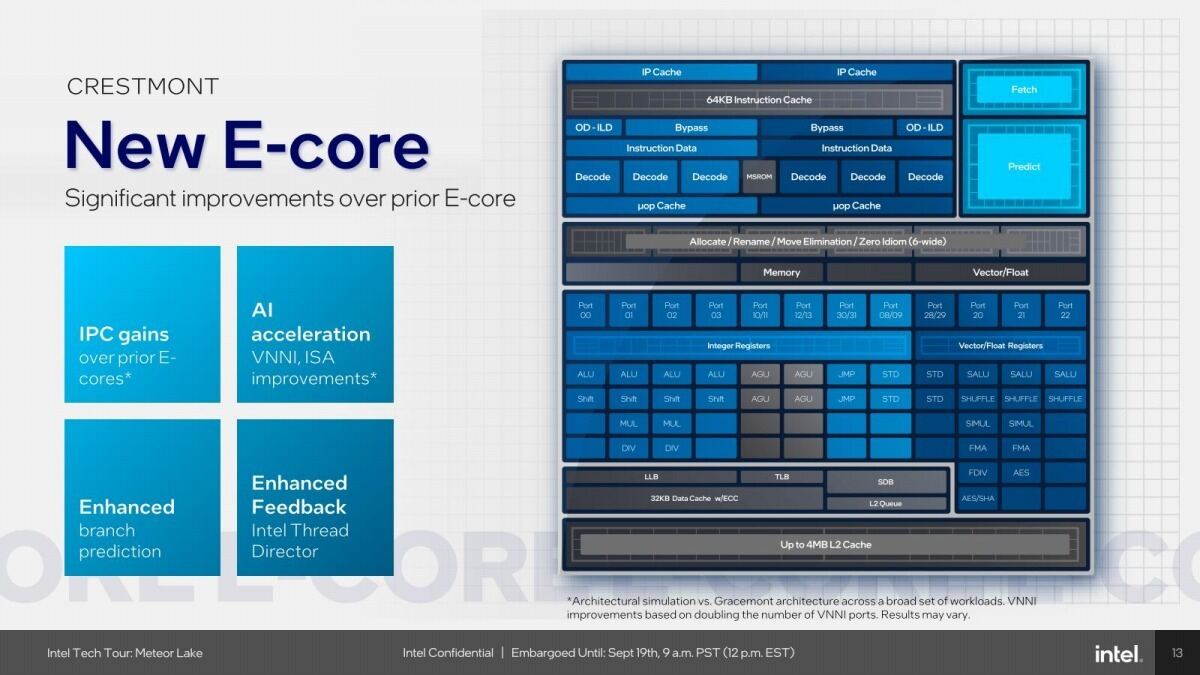

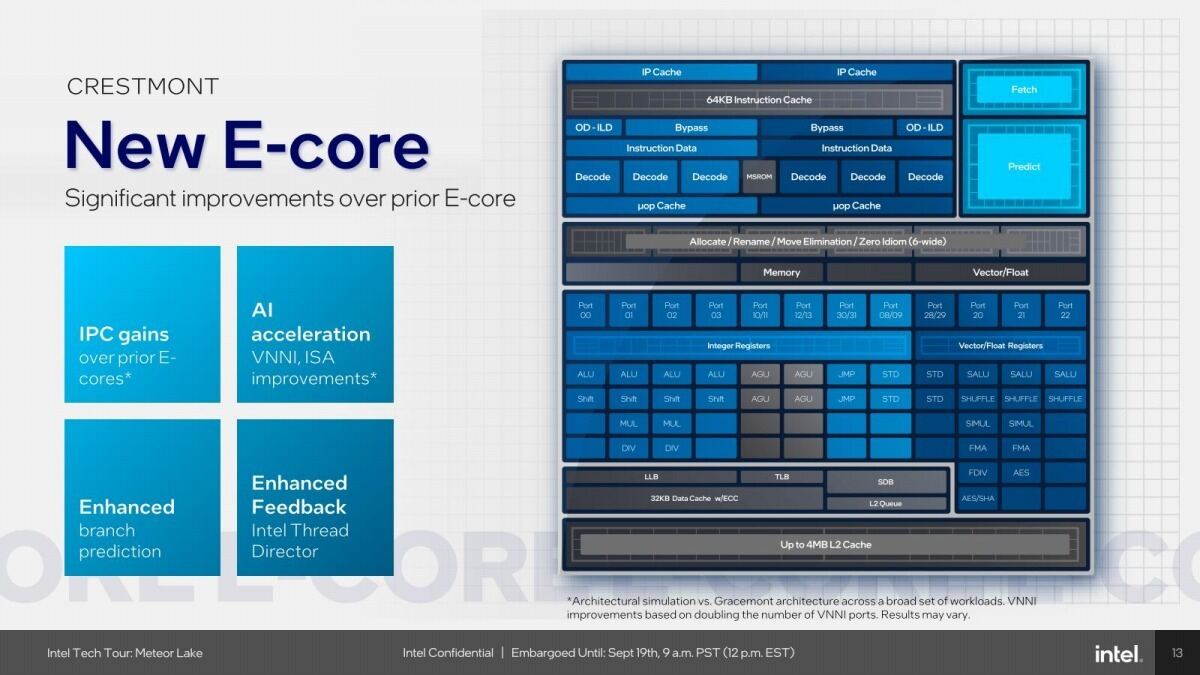

これはE-Coreについても同じだ。Meteor Lakeに搭載されるE-CoreであるCrestmontの構造(Photo04)と、同じくAlder Lakeに搭載されたGracemontの構造(Photo05)が、構造そのものには変化が無い事が判る。強いて違いを挙げれば、32KBのL1 D-CacheがECC付きになったことで、これは同じタイミングで開発されていたSierra ForestがXeon向けということでECC付きL1 D-Cacheになったのがそのまま継承されている格好と思われる。

ただVNNI周りの性能改善と分岐予測の改善、ほかにも細かい改良などが行われて、ある程度IPCは向上したものと思われる。

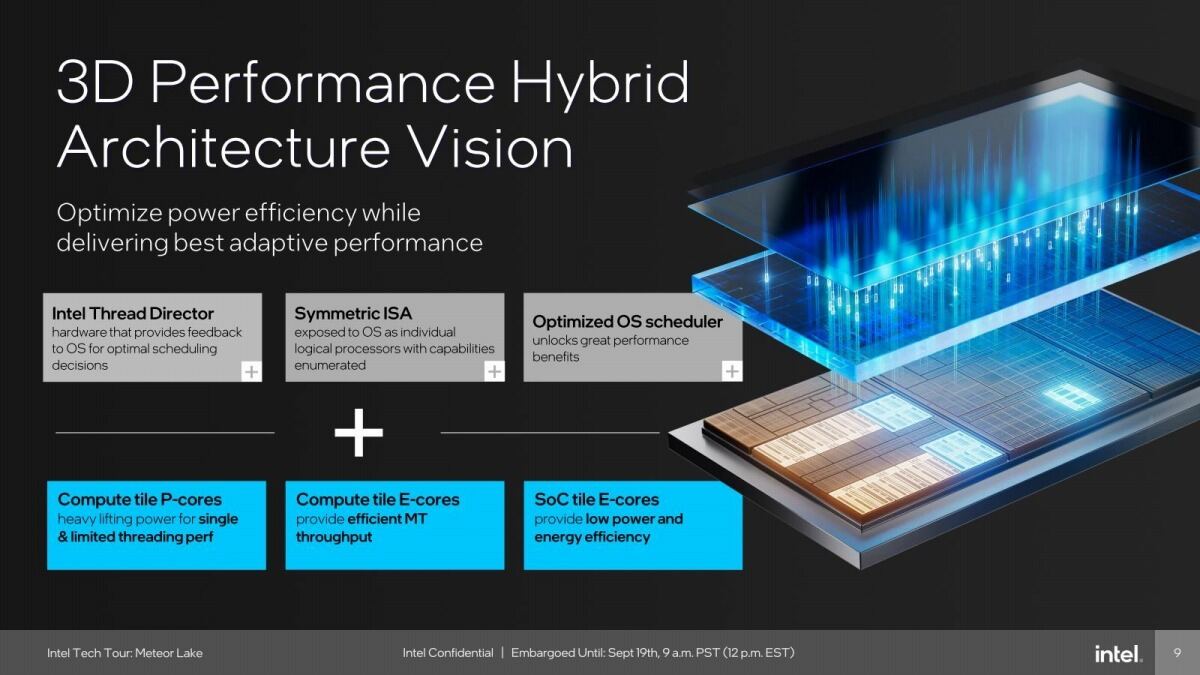

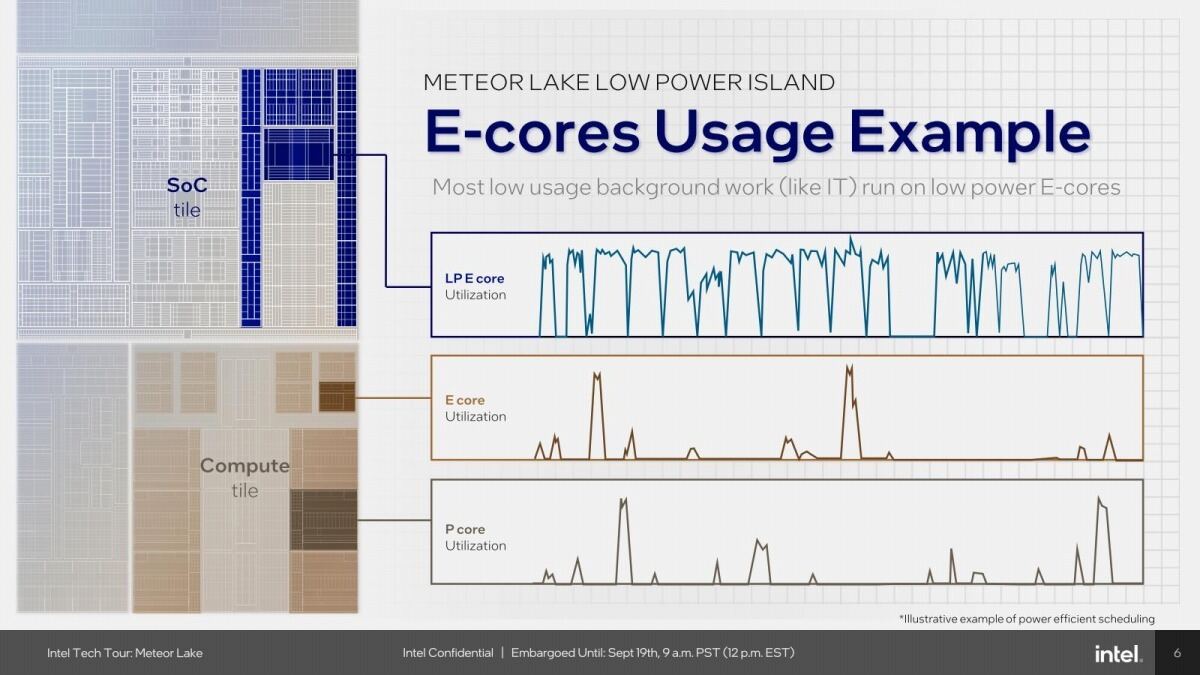

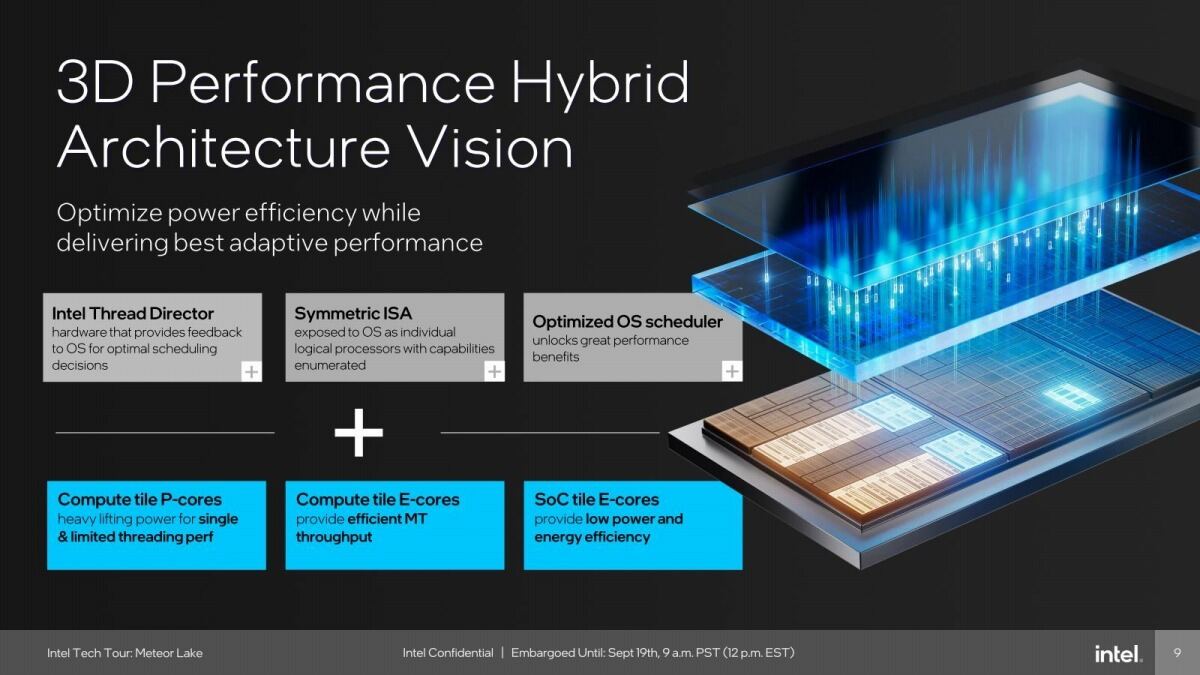

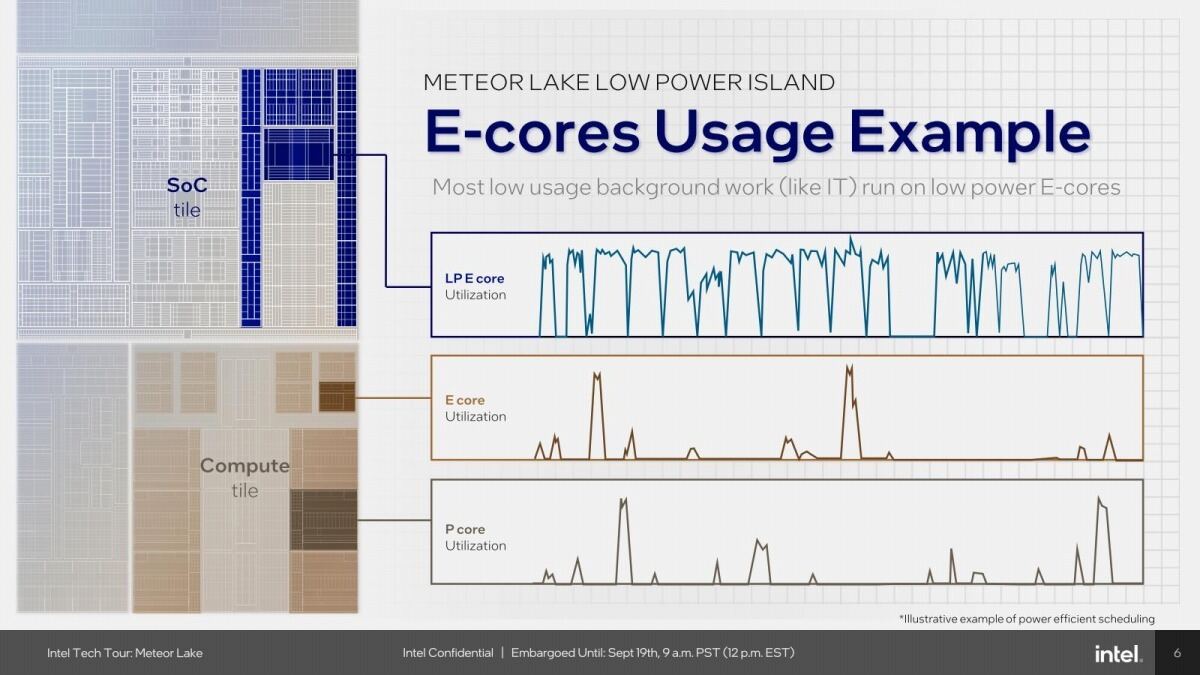

そんなわけで個々のコアそのものの構造は大きくは変わらないというか、従来の延長にあると考えられるが、大きく異なるのが内部構造である。冒頭でも書いたが、Meteor LakeはCompute Tile以外にSoC TileにもE-Coreを2つ搭載している。この目的というか使い分けであるが、それをわかりやすく示したのがこちら(Photo06)。もともとAlder Lakeの世代では、E-Coreは省電力のTask向けでP-Coreがヘビーワークロードという区分けだったのが、Raptor Lakeの世代ではE-Coreもフルにぶん回すことでMulti-Thread性能を引き上げるという、ちょっと当初とは異なる使われ方をするようになっている。Meteor Lakeではこれを一段先に進め、E-CoreはMulti-Thread向け、P-CoreはSingle-Thread向けと規定したうえで、それとは別に省電力向けのE-Coreを用意することにした。要するにAlder Lake世代のE-Coreの使い方をSoC TileのE-Coreに行わせる格好だ。

このSoC TileのE-Coreも、OSのTask Schedulingの元にある。なのでWindowsのTask Managerからは冒頭で述べたように22個の論理プロセッサが見えることになる。ただこのSoC TileのE-CoreとCompute TileのE-Coreを同列に扱ってしまうと、省電力の効果が得られない。そこでThread Directorでの扱い方も変わった(Photo07)。まずTaskはSoC TileのE-Coreで動かし、これが処理性能的に不十分であればその処理をCompute Tileに移行。ここでまずE-Coreで動作され、これで足りなければP-Coreを動かすという形になった。この結果、SoC TileのE-CoreはOSなどで要求される「細かな処理」のために常時稼働するものの、省電力性が高いコアなのでトータルの消費電力は低く抑えられる。Compute TileのE-Coreは相対的に負荷が減る格好だ(Photo08)。

SoC Tile周りはほかにも省電力向けの工夫がいろいろあるが、こちらは稿を改めて説明したい。

・「Meteor Lake」Deep Dive その4 - GPU、IO & SoC Detail

https://news.mynavi.jp/article/20231010-2789313/

・「Meteor Lake」Deep Dive その3 - AI NPU Detail

https://news.mynavi.jp/article/20231005-2785788/

・「Meteor Lake」Deep Dive その1 - Intel 4 Process Update

引き続きMeteor Lakeの構造についてご紹介したい。今回はProcessor Coreの話である。最終的に派生型とかがどの程度あるのかは判らないが、今回発表になったMeteor Lakeの基本構造は、6 P-Core +8 E-Core +2 E-Coreの16コア構成で、P-CoreはHyperThreadingが有効化されているので、OSからは22コア相当として見える形になる(Photo01)。この+2 E-Coreの話はあとでするとして、まずはそれぞれのコアのDetailである。

まずP-CoreであるRedwood Coveである。Photo02がそのパイプライン構造の概略であり、Golden Coveと比較してより効率が良くなっている、としている。Golden CoveはAlder Lakeに搭載されたもので、Raptor Lakeに搭載されているRaptor Coveも(キャッシュ容量以外は)Golden Coveと同じとされている。ではそのGolden Coveはどんなだったか? というのがこちら(Photo03)。実のところ、このレベルでいえばGolden CoveとRedwood Coveの違いは

L1命令キャッシュが32KB→64KBに増量

L2キャッシュが1.25MB→2MBに増量

といったあたりで、L2はRaptor Coveの世代ですでに増量されていたことを考えると、要するにL1命令キャッシュが増量された「だけ」という可能性も残る。もちろん実際には細かい命令のLatency削減とかバグ修正とかが行われている可能性はあるが、大きなものではないように思える。New P-coreと書いてはあるものの、基本はGolden Coveの世代を継承しており、Power Efficencyは64KBのL1命令キャッシュか、あとは細かい部分での積み重ねと思われる(プロセスの違いはArchitectual Simulationには反映されないため)。

これはE-Coreについても同じだ。Meteor Lakeに搭載されるE-CoreであるCrestmontの構造(Photo04)と、同じくAlder Lakeに搭載されたGracemontの構造(Photo05)が、構造そのものには変化が無い事が判る。強いて違いを挙げれば、32KBのL1 D-CacheがECC付きになったことで、これは同じタイミングで開発されていたSierra ForestがXeon向けということでECC付きL1 D-Cacheになったのがそのまま継承されている格好と思われる。

ただVNNI周りの性能改善と分岐予測の改善、ほかにも細かい改良などが行われて、ある程度IPCは向上したものと思われる。

そんなわけで個々のコアそのものの構造は大きくは変わらないというか、従来の延長にあると考えられるが、大きく異なるのが内部構造である。冒頭でも書いたが、Meteor LakeはCompute Tile以外にSoC TileにもE-Coreを2つ搭載している。この目的というか使い分けであるが、それをわかりやすく示したのがこちら(Photo06)。もともとAlder Lakeの世代では、E-Coreは省電力のTask向けでP-Coreがヘビーワークロードという区分けだったのが、Raptor Lakeの世代ではE-Coreもフルにぶん回すことでMulti-Thread性能を引き上げるという、ちょっと当初とは異なる使われ方をするようになっている。Meteor Lakeではこれを一段先に進め、E-CoreはMulti-Thread向け、P-CoreはSingle-Thread向けと規定したうえで、それとは別に省電力向けのE-Coreを用意することにした。要するにAlder Lake世代のE-Coreの使い方をSoC TileのE-Coreに行わせる格好だ。

このSoC TileのE-Coreも、OSのTask Schedulingの元にある。なのでWindowsのTask Managerからは冒頭で述べたように22個の論理プロセッサが見えることになる。ただこのSoC TileのE-CoreとCompute TileのE-Coreを同列に扱ってしまうと、省電力の効果が得られない。そこでThread Directorでの扱い方も変わった(Photo07)。まずTaskはSoC TileのE-Coreで動かし、これが処理性能的に不十分であればその処理をCompute Tileに移行。ここでまずE-Coreで動作され、これで足りなければP-Coreを動かすという形になった。この結果、SoC TileのE-CoreはOSなどで要求される「細かな処理」のために常時稼働するものの、省電力性が高いコアなのでトータルの消費電力は低く抑えられる。Compute TileのE-Coreは相対的に負荷が減る格好だ(Photo08)。

SoC Tile周りはほかにも省電力向けの工夫がいろいろあるが、こちらは稿を改めて説明したい。