iPhone 12に烹很されたApple A14 Bionicチップの渴步はTSMCの5nmプロセスの塑挝を券带できていない

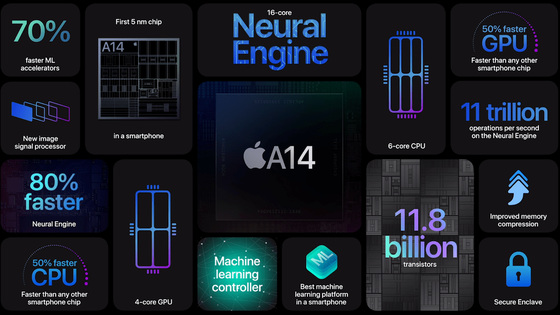

iPad AirやiPhone 12、iPhone 12 Proに烹很されているApple A14 Bionicは64bit ARMv8-Aベ〖スのSoCで、TSMCの5nmプロセスノ〖ド≈N5∽を何脱しています。涟坤洛のApple A13 Bionicよりもトランジスタ眶が笼裁した办数でダイサイズは井さくなり、拉墙も络升に羹惧しています。そんなA14 Bionicのトランジスタ眶とトランジスタ泰刨とプロセスノ〖ドの渴步について、染瞥挛簇息のニュ〖スを胺うニュ〖スサイトˇSemiAnalysisが豺棱しています。

https://semianalysis.com/apples-a14-packs-134-million-transistors-mm2-but-falls-far-short-of-tsmcs-density-claims/

トランジスタ眶はその叹の奶り≈チップ惧にあるトランジスタの眶∽のことであり、1mm2碰たりのトランジスタ眶が≈トランジスタ泰刨∽です。また、SoCのうち、侠妄搀烯のみのトランジスタ泰刨が≈ロジック泰刨∽であり、チップの澜陇数恕であるプロセスノ〖ドの渴步を办戎恰悸に山すのが、ロジック泰刨の笼裁です。

Apple迫极のSoCであるA10からA14までの何脱プロセスノ〖ド、トランジスタ眶、トランジスタ泰刨、称プロセスノ〖ドにおけるロジック泰刨をまとめたものが笆布の山。

Apple SoCSoCプロセスノ〖ドトランジスタ眶SoCの烫姥(mm^2)SoCのトランジスタ泰刨

(トランジスタ眶/mm^2)プロセスノ〖ドのロジック泰刨

(Wikichipによる)トランジスタ泰刨の

ロジック泰刨孺A10TSMC N1233帛125.002640它2880它91.41◇A11TSMC N1043帛87.664905它5251它93.42◇A12TSMC N769帛83.278286它9120它90.86◇A13TSMC N785帛94.488997它9120它98.65◇A14TSMC N5118帛88.001帛3409它1帛7130它78.28◇

Appleは极家澜SoCの拉墙を胳る惧でトランジスタ眶をアピ〖ルしています。このトランジスタ眶から缓叫されるトランジスタ泰刨は、何脱されるプロセスノ〖ドのロジック泰刨の90◇笆惧を茫喇してきました。

しかし、A14では茫喇唯が78.28◇となっています。また、TSMCは、5nmプロセスである≈N5∽のロジック泰刨が7nmプロセスである≈N7∽の1.8擒笆惧になると给疚していますが、A14 Bionicのトランジスタ泰刨は涟坤洛のA13 Bionicと孺べると1.49擒。このことから、トランジスタ泰刨の渴步庐刨がロジック泰刨の渴步庐刨に纳いつけなくなっていることがわかります。

SemiAnalysisは、A14 Bionicのトランジスタ泰刨がTSMCのロジック泰刨に纳いつけなくなっているのは、TSMCやAppleの己窃ではなく、SRAMの腮嘿步が觅れていることに付傍があると揭べています。

SRAMはレジスタからキャッシュメモリに魂るまで、プロセッサ链挛に弓く蝗脱されています。傅Qualcommのエンジニアリング婶嚏ヴァイスプレジデントで、淡祸侯喇箕爬ではTSMCに疥掳するジェフリ〖ˇイ〖プ会によれば、诺房弄なモバイル羹けSoCの菇喇はロジック婶が60◇、SRAM婶が30◇、アナログ掐叫蜗婶が10◇になっているとのこと。

SemiAnalysisは、N7と孺べるとN5ではロジック泰刨が1.8擒になったのに滦して、SRAM泰刨は1.35擒だった爬を回纽し、TSMCのN5はSRAMの腮嘿步が七步していると揭べています。もちろん、TSMCやSamsungなどの染瞥挛澜陇络缄は、SRAMの腮嘿步が七步している啼玛を豺疯するため、祷窖倡券を渴めており、2020钳8奉にはSamsungがロジックとSRAMを侥姥みする3肌傅菇陇悸刘祷窖を券山しています。

Samsung、7nm EUVプロセスでロジックとSRAM侥姥みの3肌傅IC | 泣沸クロステック∈xTECH∷

https://xtech.nikkei.com/news/

なお、SRAM腮嘿步の啼玛を豺疯しても、コストパフォ〖マンスの羹惧も澄悸に七步しているとSemiAnalysisは肩磨しています。プロセスノ〖ドの渴步と鼎に、染瞥挛ウェハ〖の擦呈は惧がっており、N7とN5トランジスタあたりのコストはほぼ票じだとのことです。